|

Школа схемотехнического проектирования устройств обработки сигналов

Занятие 14. Программируемые аналоговые интегральные схемы

Никогда не выявляйте в программе ошибки, если не знаете, что с ними дальше делать.

Руководство по системному программированию Штейнбаха

Общие сведения

В предыдущих занятиях основной упор был сделан на проектирование цифровых устройств обработки сигналов на базе ПЛИС. Тем не менее разработчики прекрасно понимают, что не цифрой единой жив человек. Современная аппаратура обработки сигналов немыслима без аналоговой предварительной обработки, преобразования данных с датчиков и формирования управляющих напряжений и токов для исполнительных элементов. В то же время уровень интеграции и степень «сапровости» аналоговых схем пока еще не достигли аналогичных показателей цифровых устройств. В этой главе делается попытка показать довольно новый класс устройств — программируемые аналоговые интегральные схемы (ПАИС, в зарубежной терминологии — FPAA, Field Programmable Analog Array).

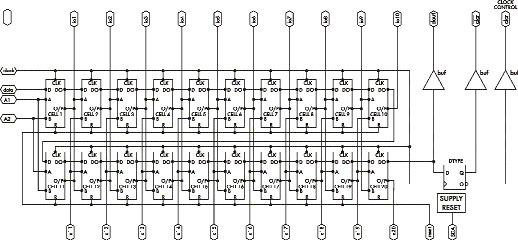

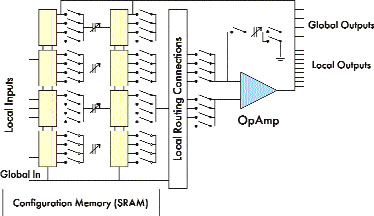

Рис. 1

Архитектуры ПАИС

Значение ПЛИС при проектировании цифровых схем не нуждается в дополнительных комментариях, поэтому абсолютно понятны попытки компаний-производителей элементной базы выпустить схожий по назначению и популярности компонент и для аналоговой схемотехники. Количество фирм-производителей ПАИС несколько меньше, чем производителей ПЛИС, тем не менее оно достаточно велико. Даже после ухода с рынка ПАИС такого гиганта, как Motorola, существуют несколько довольно крупных производителей

ПАИС. Рассмотрим архитектуры ПАИС нескольких популярных производителей.

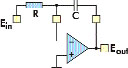

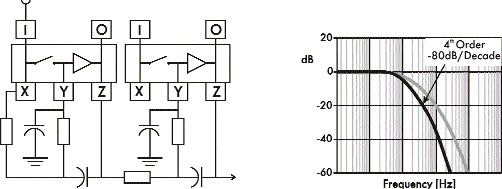

Рис. 2

Один из авторитетных производителей матричных структур — Lattice Semiconductor (www.latticesemi.com). Кстати, именно она начала впервые выпускать ПЛИС с возможностью программирования в системе (без извлечения какого-либо компонента из печатной платы) и впервые употребила соответствующую аббревиатуру ISP.

Теперь Lattice предлагает ПАИС с этой возможностью — семейство ispPAC (In-System Programmable Analog Circuit). В его состав входят микросхемы ispPAC10 и ispPAC20.

Заложенная в эту серию архитектура основывается на следующих функциональных базовых ячейках:

- инструментальный усилитель (IA);

- выходной усилитель (OA), реализованный по схе ме сумматора/интегратора;

- 2,5-вольтовый источник опорного напряжения (Reference, ИОН);

- 8-разрядный ЦАП с выходом по напряжению;

- сдвоенный компаратор (CP).

Аналоговые входы и выходы ячеек (кроме ИОН) для повышения динамического диапазона обрабатываемых сигналов выполнены по дифференциальной схеме. Подробно об этой серии ПАИС было написано в [1].

Проектирование устройств серии ispPAC поддерживается САПРом PAC-Designer. Этот пакет обеспечивает в графическом виде редактирование схемы путем проведения конкретных внутренних межсоединений и задания величин программируемых параметров, ее моделирование (к сожалению, пока только в частотной области), создание конфигурационного файла и его загрузку.

Разводку и задание значений параметров выполняют вручную. Но в системе также имеется библиотека некоторых готовых решений, в том числе и для построения активных фильтров. Процесс проектирования несложен, и результаты получаются достаточно быстро. Демонстрационную версию PAC-Designer можно скачать с сайта фирмы. С ее помощью легко разобраться в возможностях схем и оценить их пригодность для конкретной задачи.

Lattice не является единственным производителем ПАИС. Так, компания Fast Analog Solution (www.fas.co.uk), которая входит в группу ZETEX, предлагает такие микросхемы в серии TRAC. Фирма обозначает их как Field Programmable Analog Devices (FPAD).

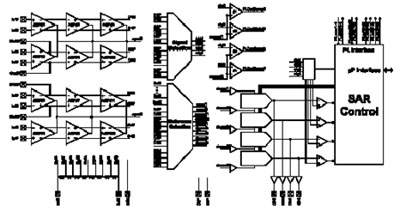

Архитектура этих ПАИС приведена на рис. 1.

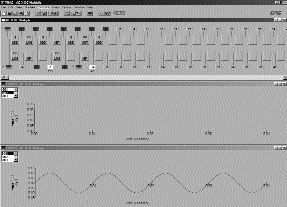

Рис. 3

Каждая ячейка содержит операционный усилитель и конфигурируемые цепи обратной связи, что позволяет реализовывать базовые блоки аналоговой обработки сигналов. Так, на рис. 2 представлен интегратор.

Следует отметить, что цепи обратной связи могут содержать как линейные, так и нелинейные элементы, что позволяет строить и функциональные преобразователи.

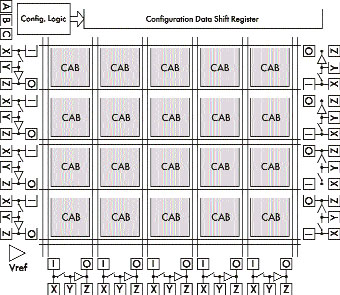

Рис. 4

Поставляемое программное обеспечение обладает достаточно широкими возможностями по вводу параметров и моделированию устройств. На рис. 3 представлено окно программы с загруженным проектом перемножителя «логарифм-антилогарифм» и

результатами его моделирования во временной области.

Рис. 5

Еще один известный производитель

ПАИС — компания Anadigm (www.anadigm.com).

Отличительная особенность ПАИС AN10E40 состоит в том, что они представляют собой матричную структуру (4ґ5 ячеек), причем каждая из ячеек выполнена на ОУ с переключаемыми конденсаторами (switched capacitor). Архитектура ПАИС AN10E40 компании Anadigm представлена на рис. 5.

Рис. 6

На рис. 6 видно, что основное применения ПАИС AN10E40 компании Anadigm — реализация фильтров и линейных устройств обработки. Пример реализации фильтра четвертого порядка показан на рис. 7.

Рис. 7

Каждая ячейка позволяет реализовать звено второго порядка. Конфигурация ПАИС может осуществляться с помощью микроконтроллера, встроенного в систему.

В данном случае ПАИС занимает определенную область в адресном пространстве контроллера, а конфигурационные данные хранятся в его памяти или постоянной памяти системы.

Конфигурация ПАИС возможна также и с применением последовательного ПЗУ.

Для отладки проектов, выполненных на ПАИС, фирма Anadigm выпускает специализированную отладочную плату, позволяющую провести отработку проекта.

Программное обеспечение AnadigmDesigner поставляется бесплатно и имеет удобные средства ввода проекта, моделирования и загрузки конфигурации.

Рис. 8

Рассмотрим пример проектирования фильтра (рис. 8)

Возможен выбор из довольно большого числа базовых узлов. Во многом процесс напоминает использование макросов в ПЛИС.

На рис. 10 представлено меню моделирования (Simulate), позволяющее задать источники сигнала и установить контрольные точки, задать параметры моделирования и начать процесс моделирования.

Рис. 9

На рис. 11 показан диалог задания параметров моделирования.

Можно задать начало и конец моделирования, а также его шаг.

Рис. 10

На рис. 12 представлена панель генератора тестового сигнала. Можно выбрать форму сигнала, задать его амплитуду и частоту, а также постоянную составляющую сигнала.

Рис. 11

Индикация процесса моделирования осуществляется с помощью осциллографа (рис. 13).

Это окно напоминает виртуальные приборы пакета LabView и функционирует подобно обычному осциллографу.

Рис. 12

Для синтеза фильтров пакет опционально может быть дополнен утилитой FilterDesigner, окно которой приведено на рис. 14.

С ее помощью можно создать IPmodul фильтра с требуемыми частотными параметрами, аппроксимацией и т.п. Утилита позволяет провести полное моделирование фильтра, задать его характеристики.

Рис. 13

Помимо чисто цифровых или чисто аналоговых программируемых структур разработаны изделия, содержащие на одном кристалле как программируемую логику, так и аналоговые элементы и микроконтроллерное ядро. К таким системам на кристалле относятся изделия фирмы SIDSA (www.sidsa.com). Изделия содержат ядро контроллера, совместимое с ядром 8051, 6 КБ ОЗУ и способное работать на тактовых частотах до 48 МГц.

Рис. 14

Каждый программируемый аналоговый блок содержит 4 дифференциальных канала, состоящих из трех ОУ с программируемым коэффициентом усиления и четырех компараторов с программируемым источником опорного напряжения (рис. 15).

Кроме того, в состав аналогового блока входят 4 ЦАП с конфигурируемой разрядностью от 8 до 10 бит и быстродействием 800 000 отсчетов в секунду.

Рис. 15

Ячейка программируемой логики состоит из комбинационного блока (Combinational Block), построенного на основе таблиц

перекодировки, последовательного блока (Sequential Block) и ресурсов трассировки.

Быстродействие ячеек составляет до

40 MГц, задержка в таблице перекодировок не более 5 нс.

В пакет поставки входит специализированное программное обеспечение, позволяющее провести ввод проекта, его моделирование и конфигурацию устройства.

Типовой маршрут проектирования с использованием ПО Sidsa показан на рис. 16. Как можно видеть, он состоит из разработки логической части проекта и программирования контроллерного ядра. Отдельно проводится разработка и конфигурация аналоговых узлов. Ввод проекта возможен как в схемном режиме, так и с использованием языков описания аппаратуры и подключения внешних модулей синтеза.

В комплект поставки входит отладочная плата, позволяющая провести отработку решений в реальной системе. Она содержит достаточное количество буферных элементов и каналов ввода-вывода для подачи необходимых тестовых сигналов.

В настоящее время имеются разнообразные программируемые аналоговые структуры, которые в значительной мере могут облегчить жизнь разработчика.

Литература

1. А. Курбатов. Программируемые аналоговые интегральные схемы. Жизнь продолжается — Компоненты и технологии, № 2, 2000.

Владимир Стешенко,

к. т. н.

steshenk@sm.bmstu.ru

|